adc <Xd>, <Xn>, <Xm>

adc就是带「进位」加法,指令中的c就是英文carry。

整个指令等价于:

(Xd, _) = Xn + Xm + PSTATE.C

也就是将寄存器Xn,寄存器Xm,PSTATE中的「进位」标志相加,将相加的结果写入寄存器Xd,但是丢弃相加产生的「进位」。

也就是说,adc指令只是使用PSTATE中的「进位」标志,但是最终结果不影响PSTATE中的「进位」标志。

上面代码中PSTATE是Process State,存储着ARM CPU运行时的一些状态。

PSTATE 中最常见的状态就是 NZCV:

N: 借位标志 - Negative Condition flag

Z: 0 - Zero Condition flag

C: 进位标志 - Carry Condition flag

V: 溢出标志 - Overflow Condition flag

要表示PSTATE中的某一标志,比如「进位」,可以写成PSTATE.C。

PSTATE除了NZCV这4个标志外,还有其他标志。

如果将PSTATE定义成一个结构体,可以表示为:

type ProcState is (

bits (1) N, // Negative condition flag

bits (1) Z, // Carry condition flag

bits (1) C, // Zero condition flag

bits (1) V, // Overflow condition flag

bits (1) D, // Debug mask bit [AArch64 only]

bits (1) A, // SError interrupt mask bit

bits (1) I, // IRQ mask bit

bits (1) F, // FIQ mask bit

bits (1) PAN, // Privileged Access Never Bit [v8.1]

bits (1) UAO, // User Access Override [v8.2]

bits (1) DIT, // Data Independent Timing [v8.4]

bits (1) TCO, // Tag Check Override [v8.5, AArch64]

bits (2) BTYPE, // Branch Type [v8.5]

bits (1) ZA, // Accumulation array [SME]

bits (1) SM, // Streaming SVE mode [SME]

bits (1) ALLINT, // Interrupt mask bit

bits (1) SS, // Software step bit

bits (1) IL, // Illegal Execution state bit

bits (2) EL, // Exception level

bits (1) nRW, // not Register Width: 0=64, 1=32

bits (1) SP, // Stack pointer select: 0=SP0, 1=SPx [AArch64 only]

bits (1) Q, // Cumulative saturation flag [AArch32 only]

bits (4) GE, // Greater than or Equal flags [AArch32 only]

bits (1) SSBS, // Speculative Store Bypass Safe

bits (8) IT, // If-then bits, RES0 in CPSR [AArch32 only]

bits (1) J, // J bit, RES0 [AArch32 only, RES0 in SPSR and CPSR]

bits (1) T, // T32 bit, RES0 in CPSR [AArch32 only]

bits (1) E, // Endianness bit [AArch32 only]

bits (5) M // Mode field [AArch32 only]

)

可以看到,PSTATE在ARM64和ARM32中不一样。有些标志在ARM64和ARM32都存在,有些却只在ARM64或者ARM32中单独存在。

同时,不同版本的ARM架构,PSTATE也不一样,比如标志BTYPE就存在ARMv8.5版本中。

按照ARM文档,在ARM32下只能通过CPSR寄存器查看PSTATE的部分标志。

ARM64想要查看PSTATE,不同的标志都有单独对应的寄存器。比如查看NZCV标志,就有NZCV寄存器,ARM64下已没有CPSR寄存器。

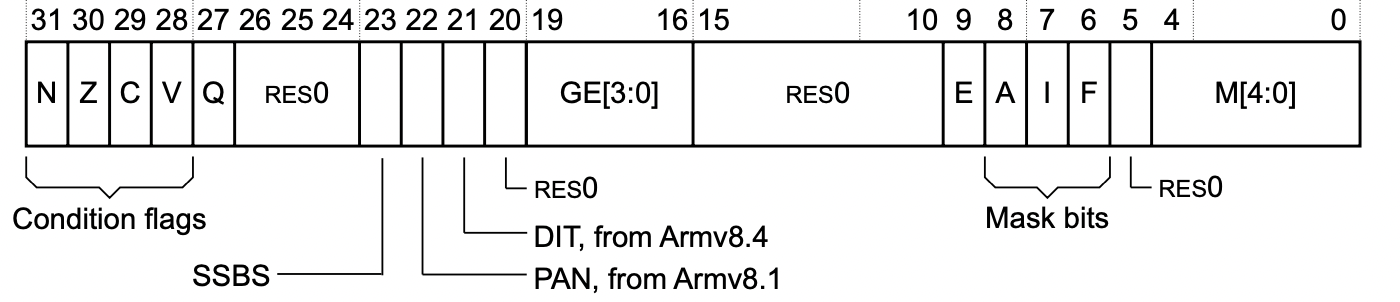

CPSR是32bit寄存器,结构如下:

但是在实践过程中,iPhone 13 pro是64bit的ARM架构处理器,但是却提供了CPSR寄存器,而不能访问比如NZCV寄存器:

(lldb) p/t $cpsr

(unsigned int) 0b01100000000000000001000000000000

(lldb) p/t $nzcv

error: <user expression 2>:1:1: use of undeclared identifier '$nzcv'

$nzcv

^

日常开发中,我们经常使用锁或者其他同步器来控制并发,那么它们的基础框架是什么呢?如何实现的同步功能呢?本文将详细用白话讲解构建锁和同步器的基础框架--AQS,并根据源码分析其原理。