https://zhuanlan.zhihu.com/p/434689028

本人lino,即将毕业的研究生,在此记录下学习过程。本次记录跟随是苏黎世邦理工大学的计算机体系结构课程。

我们需要解决许多由内存阻碍的问题,内存中数据交互存在着安全和隐私的问题,因此这对于内存来说也是一个巨大的挑战。针对这些挑战可以遵循如下的设计方向:

1、Fundamentally Secure/Reliable/Safe Architectures

2、Fundamentally Energy-Efficient Architectures

Memory-centric(Data-centric) Architectures

3、Fundamentally Low-Latency and Predictable Architectures

4、Architecture for AI/ML,Genomics,Medicine,Health

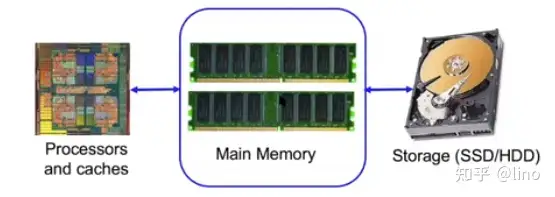

主存储器是所有计算系统中一个重要的器件,无论在server,mobile,embedded,desktop以及sensor中。

Main memory system must scale to maintain performance growth and technology scaling benefits。而提升main memory体现在size,technology efficiency,cost 以及 management algorithms。下图是一个Memory System(Onur Mutlu教授自己drew的)

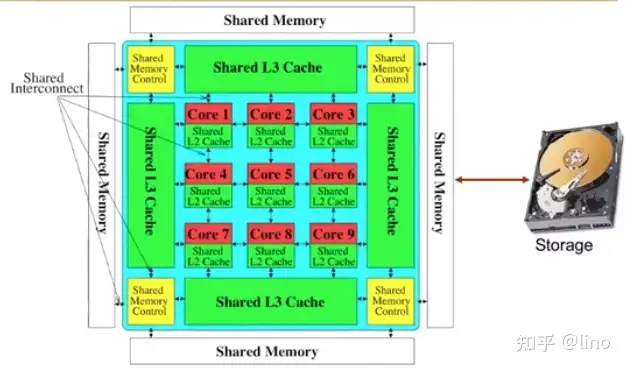

Most of the system is dedicated to storing and moving data。中间的core用来做计算用做计算单元,它们用interconnect相互连接用以搬移数据,它们连接着L2 Cache用以share or privates,L3 Cache也可以storing and moving data,但是它们shared memory controller。可以看见计算用作的运算单元其实占硬件的很小一部分,占大面积的部分的硬件用于数据的movement和存储。当然红色部分中还包括L1 cache,registers。这样大量的memory 可用来share,也会有第一篇文章的memory attacks问题。

目前DRAM and memory controllers are unlikely to satisfy all requirements。Some emmerging non-volatile memory technologier enable new opportunities : memory + storage merging。影响主存的主要的趋势如下:

1、Need for main memory capacity,bandwidth,Qos incresing

2、Main memory energy/power is a key system design concern

3、DRAM technology scaling is ending

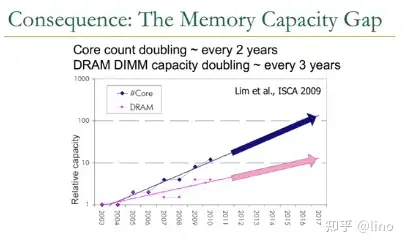

下图表明了每个核心的内存容量预计每两年下降30%

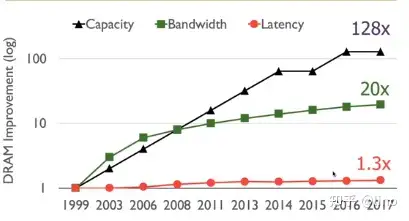

bandwidth的提升能力不如Capacity,因为虽然带宽很重要,但是在设计上会优先考虑capacity,而且capacity是很容易提升的一件事情,而延时性能的提升却很少,原因是设计的重点在于容量,并且延时的性能实际上也很难提升,

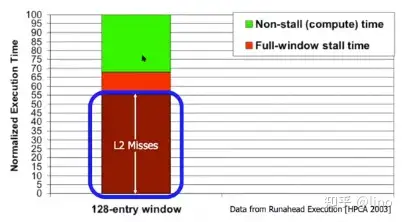

如下这幅图表明了,processors 大部分时间用来等Memory的数据,其中只有绿色部分是做计算的时间。so it's the Memory ,stupid!

而DRAM在能耗方面也消耗了大量的能量,一个原因是刷新消耗了大量能量,另一个原因是数据传输也消耗了大量能量。Google Workloads:62.7% of the total system energy is spent on data movement。

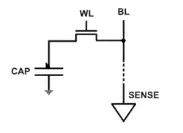

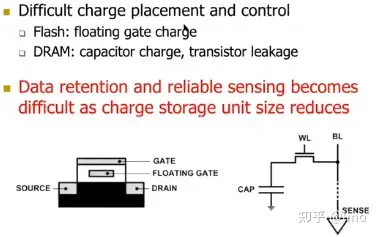

其次DRAM technology scaling is ending:DRAM will not scale easily below X nm。因为Xnm下数据的保留是个问题,有很多不同的噪音,能量增长,三极管的能量泄露等等原因。但是Scaling has provided many benefits : higher capacity(density),lower cost,lower energy。 DRAM由如下cell组成,并且Capacitor must be large enough for reliable sensing。Access transistor should be large enough for low leakage and high retention time。

Limits of Charge Memory

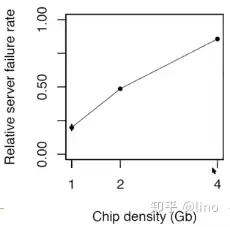

下面展示了一个Chip density和数据出错率的关系,同时也说明了As Memory Scales,It Becomes Unreliable。所以随着密集度的提高,你相应的errors也会变多。一个简单的硬件故障机制可能操作系统安全的漏洞。

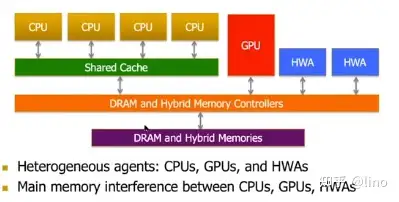

下图有着不同的混合结构,CPU,GPU,硬件加速器,Memories,这样这个设计就带来一个问题,怎么去分配资源给energies agents变得十分困难,既是一个机遇也是一个挑战。