https://zhuanlan.zhihu.com/p/436875536

本人lino,即将毕业的研究生,在此记录下学习过程。本次记录跟随是苏黎世邦理工大学的计算机体系结构课程。

本文将介绍一些宽泛的Memory的解决方案。首先是Make memory and controllers more intelligent,就是上篇文章最后提到的那个架构图,这种方案需要我们有new interfaces to memory和new functions implemented memory以及new memory architectures。Onur Mutlu教授提出的第二点是Replace or augment DRAM with a different technology,当然是maybe,大胆的猜测,New technologies and system-wide rethinking of memory。第三个观点是Embrace it:Design heterogeneous memorys(none of which are perfect)and map data intelligently across them,somebady指出数据应该存放在哪里并且怎么去使用,不同的地方使用不用的存储技术。无论哪种观点都是需要软硬件协同去工作。

Solution one:New Memory Architectures

Overcome memory shortcomings with:

Memory-centric system design

Novel memory architectures,interfaces,functions

Better waste management(efficient utilization)

这也有很多问题,目前的架构都是以处理器为中心而不是Memory,当然如果以Memory为center也会带来更大的延时这也不是我们想要的。在Memory中有很大一部分用于存储zeros,这给人一种感觉可以更高效的利用它。如果计算和数据很近的话可以摆脱数据搬移,不需要传输大量数据在memory bus上,结果也是可以reduce energy,latency,Enable reliability as well。

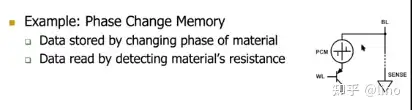

Solution two:Emerging Memory Technologies

许多新生的电阻存储器技术比DRAM更具备扩展性,因为他们可以减小特征尺寸到很小的尺寸,并且他们是非易失的。这种技术可以解决电流问题,由特殊的材料构成,数据的存储是由改变材料的phase,phase change memory --无定形和结晶的,加热进行phase的改变,不同的phase代表不同数据的编码而你读取数据是通过检测材料的resistance。

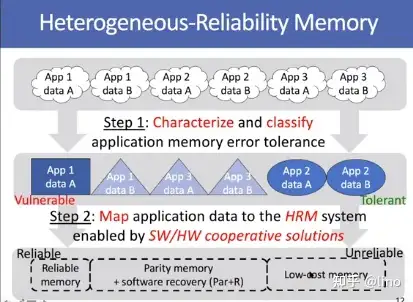

Solution three:Hybrid Memory Systems

Hybrid memory with different characteristics put together and you design the hardware and the software to manage data allocation and movement to achieve the greens as much as possible while avoiding the reds as much as possible of any technology。

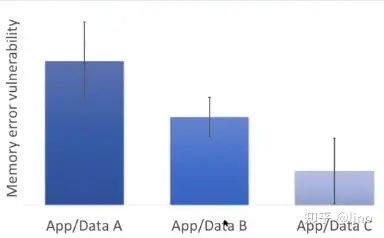

下面是教授举的一个例子,如果inject bit flips how bad it is,What is the memory error vulnerability of different types of data。

不同的Data对bit flips有不同的vulnerability。anything is stored in the dram,我们没有考虑数据对待bit flips的敏感性,只是将其存储,还是不够intelligent。如果能区分不同的vulnerability,那maybe会有更好的reliablilty。your vulnerable data goes to reliable memory and your tolerant data goes to low cost memory。

you are not going to be able to satisfy everything in the best way but you can get close with a heterogeneous system。

An Orthogonal Issue:Memory Interference(内存干扰)

problem:Memory interference between cores is uncontrolled

这会引起很多的问题unfairness,starvation,low performance,uncontrollable,unpredictable,vulnerable system。

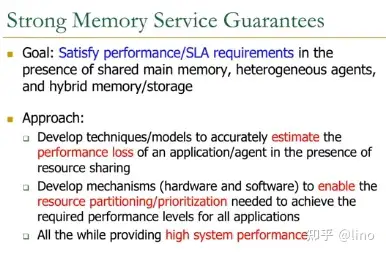

Solution:Qos-Aware Memory Systems

Hardware designed to provide a configurable fairness substrate。

Software designed to configure the resources to satisfy different Qos goals。

Qos-aware memory systems can provide predictable performance and higher efficiency。

Strong Memory Service Guarantees