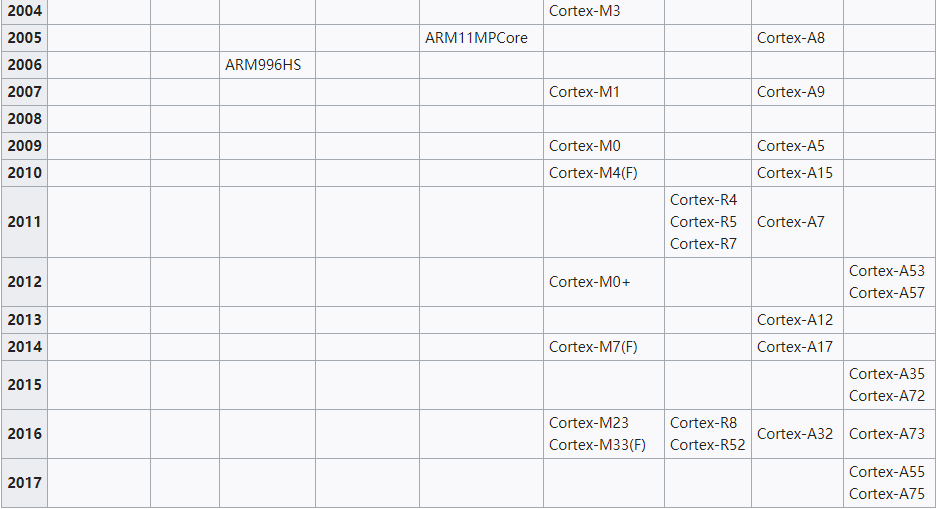

CPU发挥“大脑”的功能,负责数据的处理和运算, CPU 与 GPU 、内存、硬盘和网卡间并不能直接通信,需要通过内存控制芯片、 PCIe 控制芯片和 I/O 处理芯片等实现,这类通信协调芯片构成主板上的“芯片组”,芯片组通过各类不同总线( PCIe 总线、 USB 总线和 SPI总线等)与 CPU 相连。如果说 CPU 是“大脑”、总线就是“神经结构”,芯片组就是“神经中枢”,决定了主板总线频率和带宽,以及扩展插槽和扩展接口的种类和数量

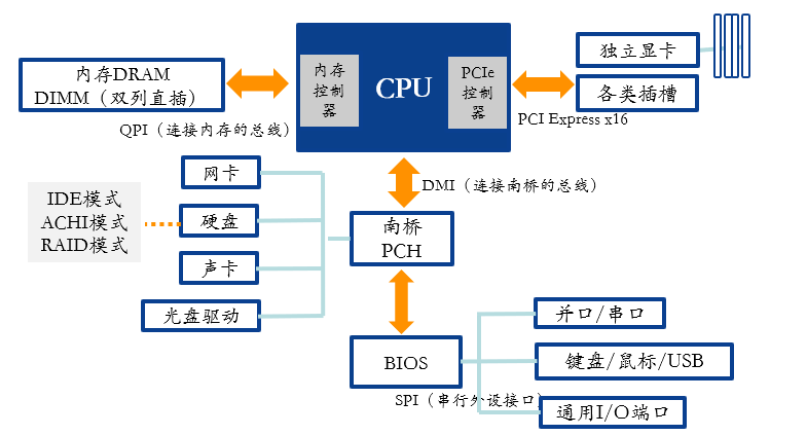

主板方面, 包括 PCIe 总线、内存、 GPU 和 SSD 。CPU 内部集成 PCIe 控制器和内存控制器, PCIe 总线点对点连接 CPU 与各类高速设备,包括 GPU 、 SSD 和网卡等,伴随 PCIe 升级至5.0 ,新一代 CPU 平台产品将兼容 PCIe5.0 标准,带动各类高速设备同步升级;而内存将从 DDR4 型号升级至DDR5 ,相关厂商或将逐步进入量产阶段。

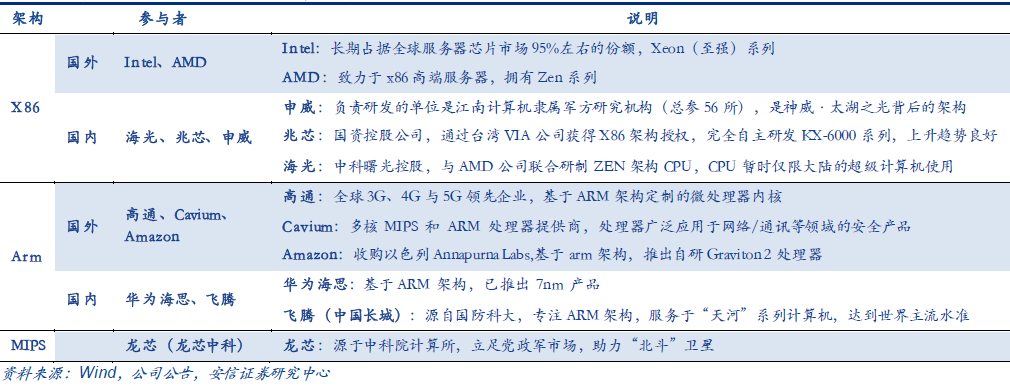

服务器CPU 架构包括 X86 、 ARM 和 MIPS 等, x86 为当前服务器 CPU 主流架构,几乎占据目前服务器全部市场份额,代表性厂商为 Intel 和 AMD 。国内方面,海光、兆芯和申威等也参与 X86 架构 CPU 的国产化替代,目前主要定位政务市场。短期来看, Intel 在服务器市场历史深厚,全球 CPU 市占率在 95% 左右 。未来 2~3 年内, Intel 仍有望保持行业龙头的地位,因而围绕其 CPU 平台的升级仍是影响服务器硬件产业链周期性变化的关键因素。

一、Intel以 Xeon 为品牌名称持续推出系列产品,产品型号命名复杂且动态变化:

1、CPU+ 芯片组 总线”构成不同的 CPU “平台”:如已经推出 Brickland 、 Grantley 、和Purley 平台,新一代 Whitley 和 Eagle Stream 预计将在 2020 年和 2021 年相继发布;

2、每一代平台产品具有多个子代,视 CPU 架构、工艺、 PCIe 控制器和内存控制器的不同 而有 差异:例如, 自 2017 年 7 月规模商用的 Purley 平台包括 SkyLake 和 CascadeLake两代,均采用 14nm 工艺最高 28 核心,但是支持的内存通道数从 6 通道升级至 8 通道, P CI e3. 0接口数增加。

3、不同平台的各个子代拥有多种型号 名称 2017 年 Purley 平台将产品型号 命名方式由此前连续使用四代的 E7 E5 变为“ 至强可扩展处理器( Intel Xeon Scalable Processor SP系列型号按 铂金( Platinum )、金 Gold)、银 Silver )、铜 Bronze 定义 。

二、ARM架构

1978年12月5日,物理学家赫尔曼·豪泽(Hermann Hauser)和工程师Chris Curry,在英国剑桥创办了CPU公司(Cambridge Processing Unit),主要业务是为当地市场供应电子设备。

1979年,CPU公司改名为Acorn计算机公司。

起初,Acorn公司打算使用摩托罗拉公司的16位芯片,但是发现这种芯片太慢也太贵。"一台售价500英镑的机器,不可能使用价格100英镑的CPU!"他们转而向Intel公司索要80286芯片的设计资料,但是遭到拒绝,于是被迫自行研发。(Intel会不会为当年的这个决定后悔万分?)

1985年,Roger Wilson和Steve Furber设计了他们自己的第一代32位、6M Hz的处理器,用它做出了一台RISC指令集的计算机,简称ARM(Acorn RISC Machine)。这就是ARM这个名字的由来。

RISC的全称是"精简指令集计算机"(reduced instruction set computer),它支持的指令比较简单,所以功耗小、价格便宜,特别合适移动设备。早期使用ARM芯片的典型设备,就是苹果公司的牛顿PDA。

1990年11月27日,Acorn公司正式改组为ARM计算机公司。苹果公司出资150万英镑,芯片厂商VLSI出资25万英镑,Acorn本身则以150万英镑的知识产权和12名工程师入股。公司的办公地点非常简陋,就是一个谷仓。

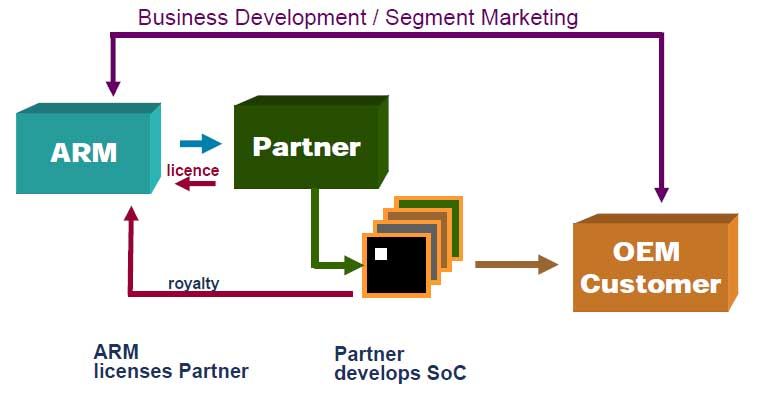

公司成立后,业务一度很不景气,工程师们人心惶惶,担心将要失业。由于缺乏资金,ARM做出了一个意义深远的决定:自己不制造芯片,只将芯片的设计方案授权(licensing)给其他公司,由它们来生产。正是这个模式,最终使得ARM芯片遍地开花,将封闭设计的Intel公司置于"人民战争"的汪洋大海。

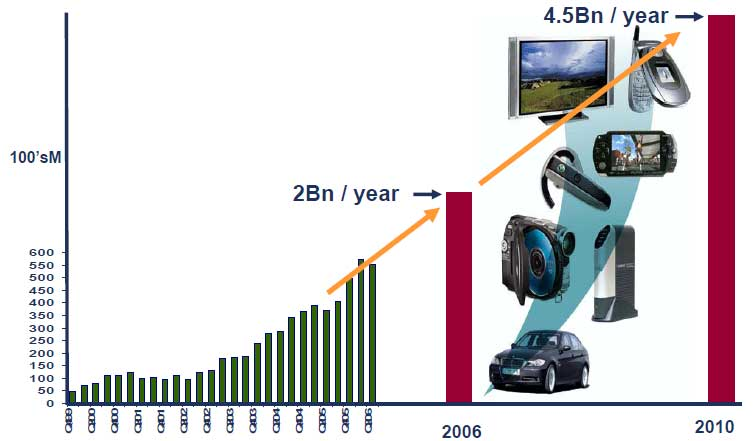

20世纪90年代,ARM公司的业绩平平,处理器的出货量徘徊不前。但是进入21世纪之后,由于手机的快速发展,出货量呈现爆炸式增长,ARM处理器占领了全球手机市场。2006年,全球ARM芯片出货量为20亿片,2010年预计将达到45亿片。

2007年底,ARM的雇员总数为1728人,持有专利700项(另有900项正在申请批准中),全球分支机构31家,合作伙伴200家,年收入2.6亿英镑。

2011年,ARM公司宣布收购了Keil公司。Keil公司是一家业界领先的微控制器(MCU)软件开发工具的独立供应商

展望未来,即使Intel成功地实施了Atom战略,将x86芯片的功耗和价格大大降低,它与ARM竞争也将非常吃力。因为ARM的商业模式是开放的,任何厂商都可以购买授权,所以未来并不是Intel vs. ARM,而是Intel vs. 世界上所有其他半导体公司。那样的话,Intel的胜算能有多少呢?

三、RISC和CISC架构

RISC:精简指令集处理器,Reduced Instruction Set Computer

RISC结构简单,选取了使用频率高的简单指令,指令长度固定,多为单周期指令在功耗、体积、价格等方面有很大优势,多用于嵌入式领域

首先,我们需要摒弃一些非常明显的误解。因为RISC的意思是简化指令集计算机(Reduced Instruction Set Computer),所以很多人认为RISC处理器只是一个没有多少指令的CPU。如果是这样的话,那么6502处理器将是有史以来最RISCy的处理器之一,它只有56条指令。甚至英特尔8086也可以算作RISC处理器,因为它只有81条指令。即使是后来的Intel 80286也只有大约100条指令。RISC-V是基于RISC原理建立的免费开放指令集架构(ISA),V是罗马字母,代表第五代RISC(精简指令集计算机),可读作RISC-FIVE。

四、CISC架构

1、什么是CISC架构

CISC方法试图最小化每个程序的指令数量,从而牺牲每个指令的周期数量。基于CISC体系结构的计算机旨在降低内存成本。因为,大型程序需要更多的存储空间,因此增加了内存成本,并且大型内存变得更加昂贵。为了解决这些问题,可以通过将操作数量嵌入单个指令中来减少每个程序的指令数量,从而使指令更加复杂。侧重于硬件执行指令的功能性,CISC指令及处理器的硬件结构复杂,CISC指令复杂,指令长度与周期不固定,在处理能力上有优势。

2、CISC处理器案例

IBM 370/168:于1970年问世。CISC设计是一个32位处理器和四个64位浮点寄存器。

VAX 11/780:CISC设计是32位处理器,它支持Digital Digital Corporation提供的许多寻址模式和机器指令。

英特尔80486:于1989年发布,它是CISC处理器,其指令长度从1到11不等,将有235条指令。

3、CISC体系结构的特征

1.指令解码逻辑将很复杂。

2.需要一条指令来支持多种寻址模式。

3.较少的芯片空间足以用于通用寄存器,以直接在存储器上操作0的指令。

4.各种CISC设计都为堆栈指针设置了两个特殊的寄存器,用于处理中断等。

5.MUL被称为“复杂指令”,需要程序员来存储功能。

4、CISC体系结构的优点

1.微编程是易于实现的汇编语言,并且比硬接线控制单元便宜。

2.对新指令进行微编码的简便性使设计人员可以使CISC机器向上兼容。

3.随着每条指令变得更加完善,可以使用更少的指令来执行给定任务。

5、CISC体系结构的缺点

1.由于不同指令占用的时钟时间不同,因此机器的性能会降低

2.即使在现实中有各种专门的指令甚至很少使用,在典型的编程事件中也仅使用现有指令的20%。

3.ISC指令将条件代码设置为每条指令的副作用,此设置需要花费一些时间-并且随着后续指令更改条件代码位-因此,编译器必须在发生这种情况之前检查条件代码位。

RISC和CISC,究竟有何不同? 参考文献:https://baijiahao.baidu.com/s?id=1732615672771252706&wfr=spider&for=pc

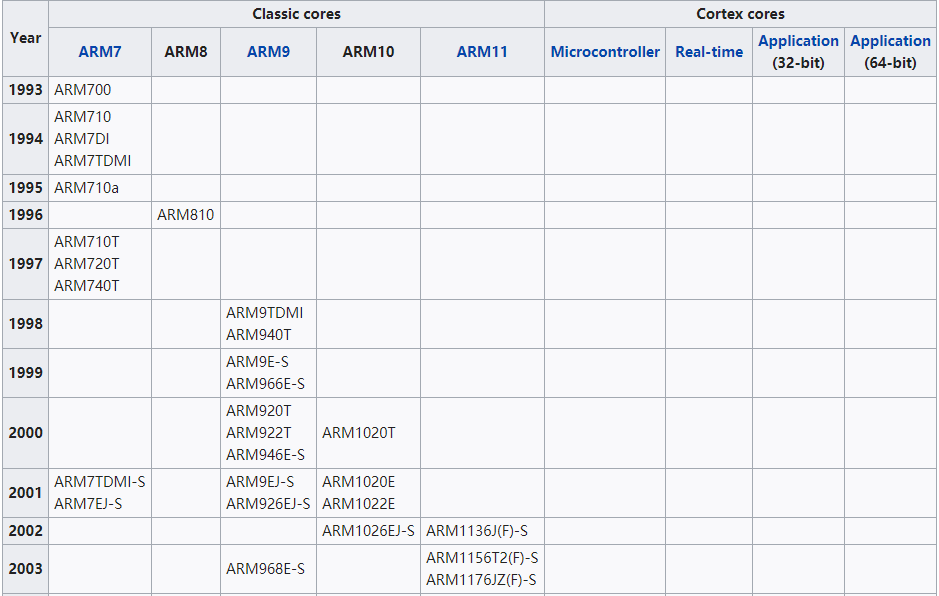

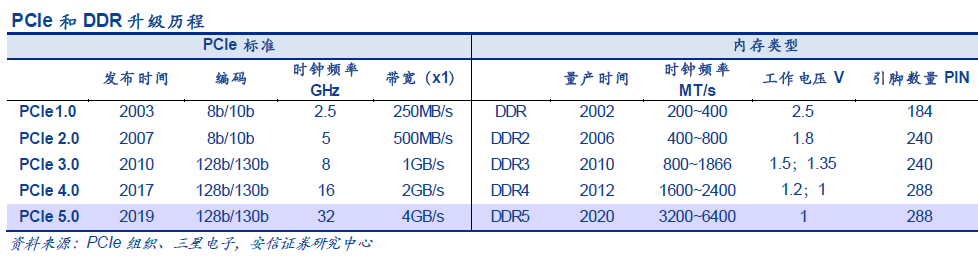

ARM产品线

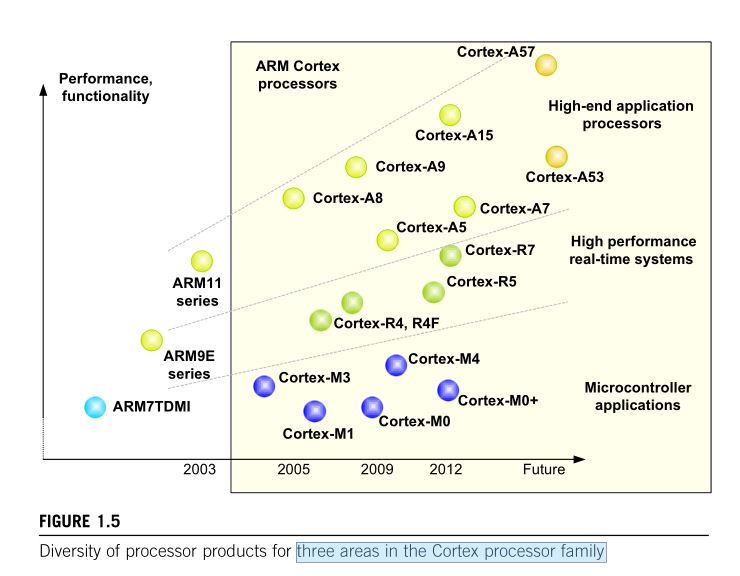

ARM11以后的产品改用Cortex命名,并分成A、R、M三个分支,旨在为各种不同的市场提供服务

Cortex-A: 面向尖端的基于虚拟内存的操作系统和用户应用

Cortex-R: 实时处理器为要求可靠性、容错功能和实时响应的嵌入式系统提供高性能解决方案

Cortex-M: 针对成本和功耗敏感的MCU和终端应用,一般不跑操作系统

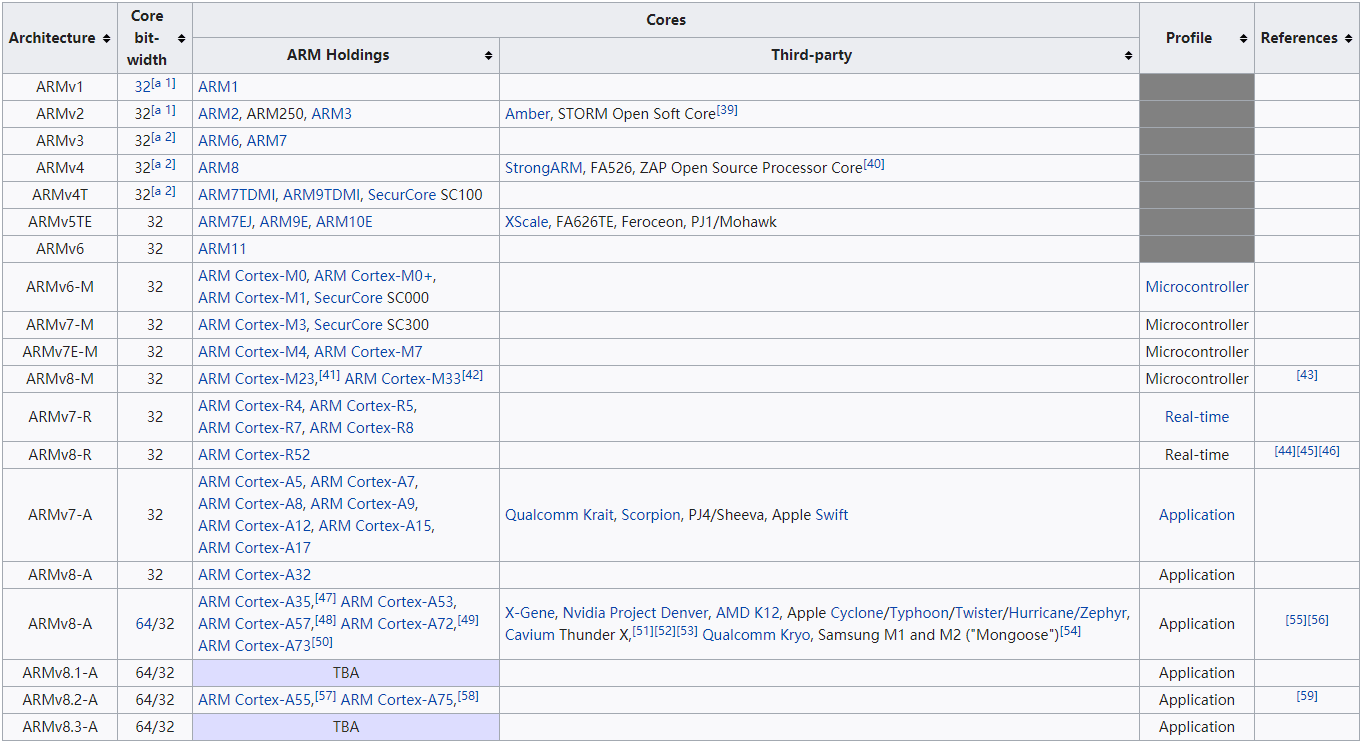

ARM架构和ARM内核

ARM处理器与架构对应表

ARM核对应的时间表