原标题:台积电3纳米成功量产:未来与三星仍将决战鳍式场效晶体管(FinFET)

来源:曲博科技教室

台积电在2022Q4高调宣布量产3纳米鳍式场效晶体管制程,是由原本的N3改良为N3B 制程良率较低的大约60~70%,较高的大约70~80%,表现相当亮眼,而计划在2023Q2或Q3量产的3纳米(N3E)制程良率更达80%以上, 而且价格更低更有竞争力。 反观三星早在2022Q2就宣布量产3纳米环绕栅极场效晶体管(GAAFET),但是被韩国媒体爆料良率只有20%,使得台积电3纳米制程大胜三星,到底FinFET 与G AAFET有什么不同? 未来三星又会如何应对呢?

什么是集成电路(IC:Integrated Circuit)?

将电的主动元件(二极管、晶体管)与被动元件(电阻、电容、电感)缩小以后,制作在硅晶圆或砷化镓晶圆上,称为“集成电路(IC:Integrated Circuit)”,其中”集成(Integrated)”与”电路(Circuit)”是指将许多电子元件堆积起来的意思。

将电子产品打开以后可以看到印刷电路板(PCB:Printed Circuit Board)如图一所示,上面有许多长得很像”蜈蚣”的集成电路(IC),集成电路的尺寸有大有小,我们以处理器为例边长大约20 毫米(mm),上面一小块正方形称为“芯片(Chip)”或“晶粒(Die)”,晶片边长大约10毫米(mm), 晶片上面密密麻麻的组件称为“晶体管(Transistor)”,晶体管边长大约100纳米(nm),而晶体管上面尺寸最小的结构称为“栅极长度(Gate length)”大约10纳米(nm),这个就是我们常听到的台积电“10纳米制程”。

图一 由晶体管(Transistor)组成芯片(Chip)再封装成集成电路(IC)。

资料来源:曲博科技教室。

什么是场效晶体管(FET:Field Effect Transistor)?

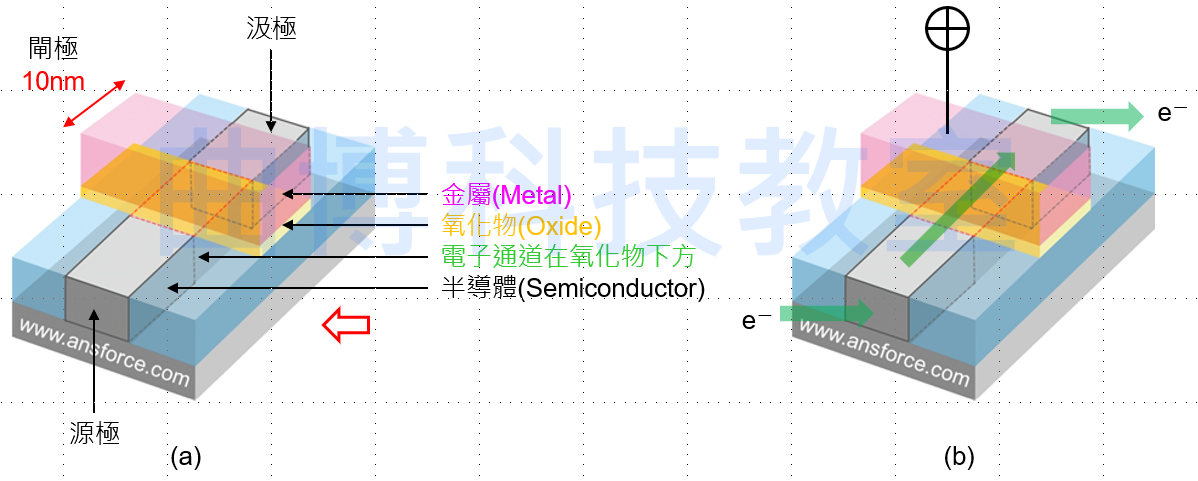

晶体管的种类很多,先从大家耳熟能详的”MOS”来说明。 MOS的全名是”金属氧化物半导体场效晶体管(MOSFET:Metal Oxide Semiconductor Field Effect Transistor)”, 构造如图二所示,左边灰色的区域叫做”源极(Source )”,右边灰色的区域叫做”漏极(Drain)”,中间有块金属(红色)突出来叫做”栅极(Gate)”,栅极下方有一层厚度很薄的氧化物 (黄色),因为中间由上而下依序为金属(Metal)、氧化物(Oxide)、半导体(Semiconductor), 因此称为”MOS”。

图二金属氧化物半导体场效晶体管(MOSFET)的结构与工作原理。

资料来源:曲博科技教室。

MOSFET的工作原理很简单,电子由左边的源极流入,经过栅极下方的电子通道,由右边的漏极流出,中间的栅极则可以决定是否让电子由下方通过,有点像是水龙头的开关一样,因此称为”栅”; 电子是由源极流入,也就是电子的来源,因此称为”源”; 电子是由漏极流出,看看说文解字里的介绍:汲者,引水于井也,也就是由这里取出电子,因此称为”汲”。

➩当栅极不加电压,电子无法导通,代表这个组件处于”关(OFF)”的状态,我们可以想像成这个位是0,如图二(a)所示;

➩当栅极加正电压,电子可以导通,代表这个组件处于”开(ON)”的状态,我们可以想像成这个位是1,如图二(b)所示。

MOSFET是目前半导体产业最常使用的一种”晶体管(Transistor)”,科学家将它制作在硅晶圆上,是数字讯号的最小单位,我们可以想像一个 MOSFET代表一个0或一个1,就是电脑里的一个”比特(bit)”。 电脑是以0与1两种数字讯号来运算,我们可以想象在硅芯片上有数十亿个MOSFET,就代表数十亿个0与1, 再用金属导线将这数十亿个MOSFET的源极、漏极、栅极连结起来,电子讯号在这数十亿个0与1之间流通就可以交互运算,最后得到我们想要的加、减、乘、除运算结果, 这就是电子计算机或电脑的基本工作原理。 晶圆厂像台积电、联电,就是在硅晶圆上制作数十亿个MOSFET的工厂。

栅极长度: 半导体制程进步的关键

在图二的MOSFET 中,”栅极长度(Gate length)”大约10纳米,是所有构造中最细小也最难制作的,因此我们常常以栅极长度来代表半导体制程的进步程度,这就是所谓的”制程节点(Node) “。

栅极长度会随制程技术的进步而变小,从早期的0.18、0.13微米,进步到90、65、45、22、 14纳米,到目前最新的制程10、7、5、3纳米,甚至未来的2纳米。 当栅极长度愈小,则整个MOSFET就愈小,而同样含有数十亿个MOSFET的芯片就愈小,封装以后的集成电路(IC)就愈小,最后做出来的手机就愈小罗!

但是要特别留意,并不是所有的晶体管都必须便用先进制程,而是要看不同元件需要的特性来决定,目前集成电路(IC)依照特性主要分为三大类:

➩数字集成电路(Digital IC):可以进行运算或储存,例如:处理器(CPU)或内存(DDR),只要承受很小的电压或电流,栅极长度愈小愈好 ,可以做到10nm(纳米)以下。

➩模拟集成电路(Analog IC):可以进行讯号放大与调变,例如:功率放大器(Power amplifier)、音频放大器(A udio amplifier),必须承受较大的电压或电流,栅极长度较大,可以做到100nm(纳米)以下。

➩功率集成电路(Power IC):可以进行电源转换,例如:功率晶体管可以将220V的交流电转换成1 10V的直流电,必须承受更大的电压或电流(功率),可以做到1μm(微米)=100 0nm(纳米)以下。

鳍式场效晶体管(FinFET):将半导体制程带入新境界

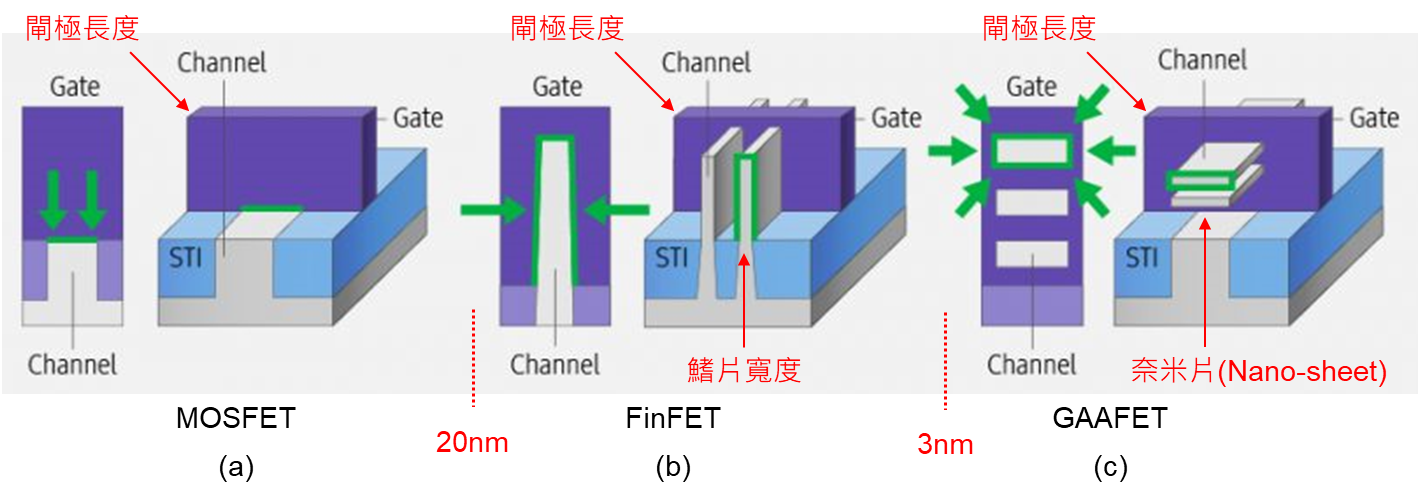

MOSFET的结构发明以来到现在已使用超过四十年,当栅极长度缩小到20纳米以下的时候遇到了许多问题,其中最麻烦的就是当栅极长度愈小,源极和漏极的距离就愈近,栅极下方的氧化物也愈薄,电子有可能偷偷溜过去产生”漏电(Leakage) “; 另外一个更麻烦的问题,原本电子是否能由源极流到漏极是由栅极电压来控制的,但是栅极长度愈小,则栅极与通道之间的接触面积愈小,如图三(a)绿色箭头所示,也就是栅极对通道的影响力愈小,要如何才能保持栅极对通道的影响力(接触面积) 呢?

因此美国加州大学伯克莱分校胡正明、Tsu-Jae King-Liu、Jeffrey Bokor等三位教授发明了”鳍式场效晶体管(FinFET:Fin Field Effect Transistor)”,把原本 2D构造的MOSFET改为3D的FinFET,如图三(b)绿色箭头所示,因为构造很像鱼鳍 ,因此称为”鳍式 (Fin)”。 由图中可以看出原本的源极和漏极拉高变成立体板状结构,让源极和漏极之间的通道变成板状,则栅极与通道之间的接触面积变大了!

这样一来即使栅极长度缩小到20纳米以下,仍然保留很大的接触面积,可以控制电子是否能由源极流到漏极,因此可以更妥善的控制电流,同时降低漏电和动态功率耗损,所谓动态功率耗损就是这个FinFET由状态0变1 或由1变0时所消耗的电能,降低漏电和动态功率耗损就是可以更省电的意思啰!

图三 晶体管的演进过程。

资料来源:wccftech.com/samsung-makes-the-first-3nm-gaafet-semiconductor。

值得注意的是,在成熟制程MOSFET里”栅极长度”代表”制程节点”,但是到了先进制程FinFET上指的其实是概念上的”平均长度”,只能当作是”商品名称”,而不是真的栅极长度, 因此”几纳米”是厂商自己定义的,厂商说是几纳米它就是几纳米,而在台积电3纳米制程里比较”接近”3纳米的结构其实是图三里的”鳍片宽度”,因为这是 所有构造中最细小也最难制作的。

环绕栅极场效晶体管(GAAFET):未来先进制程的发展方向

大家猜猜,当栅极长度缩小到3纳米以下的时候,还有什么办法可以增加栅极与通道之间的接触面积? 就是栅极把电子通道完全包围起来,如图三(c)所示,称为环绕栅极场效晶体管(GAAFET:Gate All Around Field Effect Transistor),原理其实很简单,就是增加栅极与电子通道的接触面积,可以增加栅极控制效果。

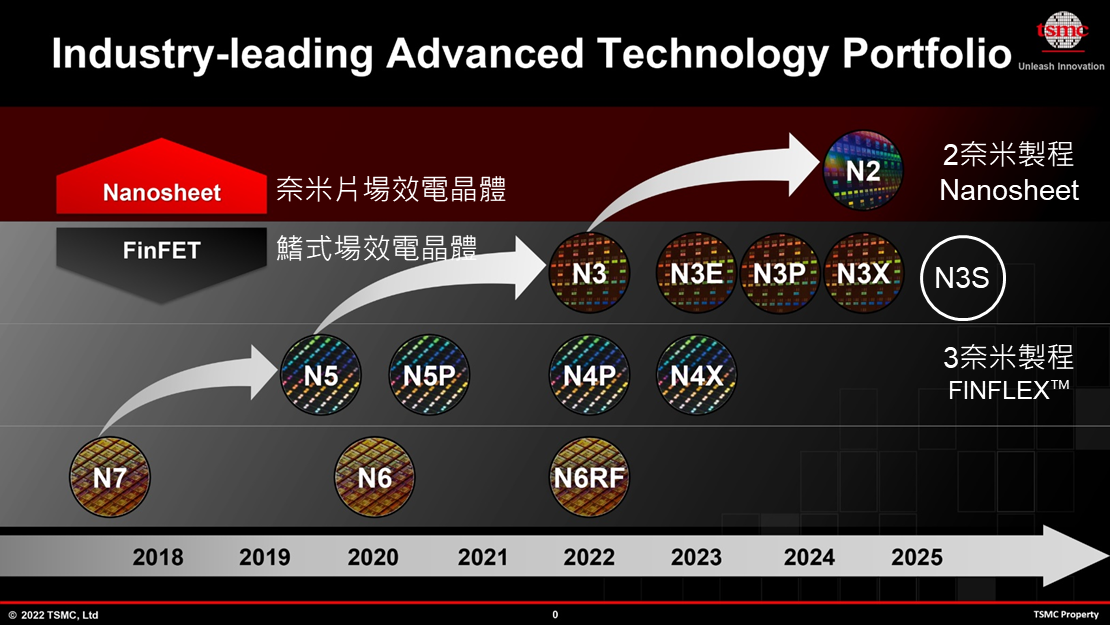

由图四可以看出,台积电与三星同时在2018年量产7纳米,英特尔在2021年量产落后三年; 台积电与三星同时在2020年量产4纳米,英特尔在2022年量产落后二年; 台积电与三星同时在2022年量产3纳米,英特尔计划在2023年量产落后一年,因此英特尔并没有大家想象的落后很多,当然宣布量产是一回事,良率多高又是另一回事, 目前进度与良率都领先的只有台积电一家,这也是台积电最大的优势。

图四 台积电与竞争对手的制程节点时间表。

资料来源:英特尔(Intel)。

值得注意的是,三家公司都把2纳米的日程压在2025年,而且都是使用GAAFET,里面有两个重要的含义,以前每一代制程大约只需要2年,但是先进制程困难度愈来愈高, 因此必须3年才行,这代表未来台积电进步将更困难,而竞争对手追上来相对比较容易,这是台积电未来必须面对的问题。

此外,三星在2022Q2量产3纳米使用新型的GAAFET,但是台积电到2022Q4才量产3纳米使用旧型的F inFET,乍看之下是确实是三星弯道超车,但是三家公司2纳米都必须使用GAAFET,因此三星比台积电与英特尔多了3年的量产经验,这是三星冒险在 3纳米使用GAAFET的主要原因,未来是不是有机会弯道超车?

台积电与三星仍将决战鳍式场效晶体管(FinFET)

环绕栅极场效晶体管(GAAFET)的制程非常复杂,比鳍式场效晶体管(FinFET)困难许多,因此国外媒体报道三星3纳米GAAFET制程良率仅20%, 这个其实并不令人惊讶,但是三星高层指出,三星3纳米制程良率已达”完美水平”且毫不迟疑开发第二代3纳米制程,事实如何就让我们拭目以待吧!

其实GAAFET良率根本很难提高,因此三星未来可能的做法就是回头使用FinFET制做3纳米,反正厂商说这个是几纳米它就是几纳米,因此我大胆预言:台积电与三星仍将决战FinFET。 为什么GAAFET良率根本很难提高,这个用文章说不清楚,有兴趣的人可以关注我们观看视频。(三星宣布量产3纳米! 是真的超车台积电? 还是真正的苦难才刚开始? )

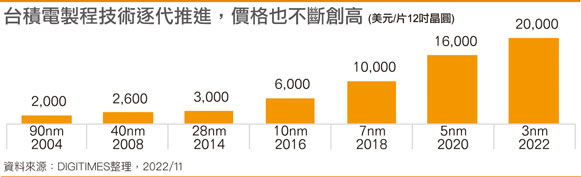

根据国外媒体的报道,高通(Qualcomm)与联发科(MediaTek)还不确定是否会在2023年使用台积电3纳米制程代工手机芯片,因此苹果有可能是2023年唯一采用台积电3纳米制成技术的厂商。 而高通与联发科之所以犹豫是否采用台积电3纳米制程的关键在于3纳米的成本极高,台积电从10纳米制程开始,每片晶圆销售价格持续上涨,7纳米一片12寸晶圆大约10,000美元 ,到3纳米一片12寸晶圆大约20,000美元,用的还是FinFET,那么到 2025年2纳米一片12吋晶圆要不要接近30,000美元? 这么贵的东西客户接受吗?

图五 台积电不同制程节点的价格预估。

资料来源:Digitimes整理。

未来三年台积电3纳米制程仍然领先全球

台积电3纳米制程(N3)改良后的 N3B已经顺利在2022Q4量产,但是未来还有下面几个衍生的 制程节点,如图六所示:

➩N3E:牺牲尺寸成全良率、效能、功耗,2023Q2或Q3量产。

➩N3P:制造工艺的性能增强版本,量产时间未定。

➩N3S:缩小尺寸的密度增加版本,量产时间未定。

➩N3X:超高性能的超频版本,量产时间未定。

由于GAAFET困难度高,成本更高,大家是否能顺利在2025年量产还是未知数,因此可以预期3纳米制程仍然是未来三年各家厂商竞争的主要标的,会使用很长一段时间, 台积电利用3纳米衍生的制程节点,仍然能够领先全球,比较令人忧心的还是美国补助英特尔、台积电、三星到美国设厂,大约都是在 2024或2025年量产,可能对先进制程产生供过于求的问题,这是比较有风险的地方,值得大家留意。

图六 台积电先进制程路线图。

资料来源:台积电(TSMC)。

曲博科技教室授权发布。

文章来自:https://www.eet-china.com/