https://zhuanlan.zhihu.com/p/615344155复制

01

ARM:3A大作

将 CPU 的设计与制造相分离的代工模式,给 AMD 提供了高度的灵活性。第二、三代 EPYC 处理器可以相对自由的选择不同的制程来匹配芯片设计的具体需求,客观上起到了帮助 AMD“以小博大”,从英特尔手中持续抢下市场份额的作用。

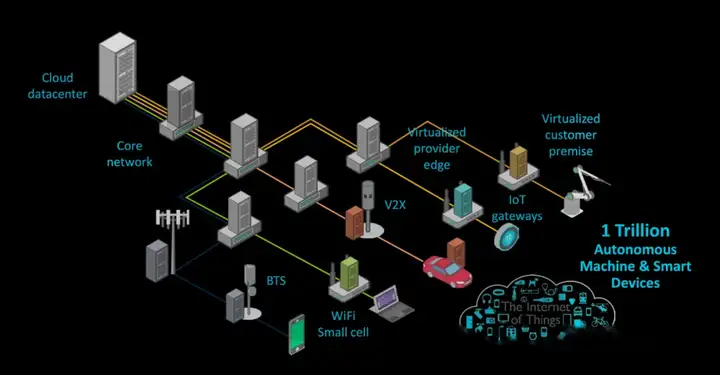

不过,这个灵活性的获益者更多在于 AMD 自身。超大规模用户如 AWS 和阿里云不满足于主要调整核心数、运行频率和 TDP 等指标的传统定制,希望对 CPU 设计有更多的自主权;又或者,新兴 CPU 供应商如 Ampere(安晟培)要选择适用的技术路线……Arm 几乎是服务器 CPU 市场上唯一的答案。

如果说台积电帮助解决 CPU 的制造问题,那么 Arm 帮助解决 CPU 的设计问题。

Cortex 孵化 Neoverse

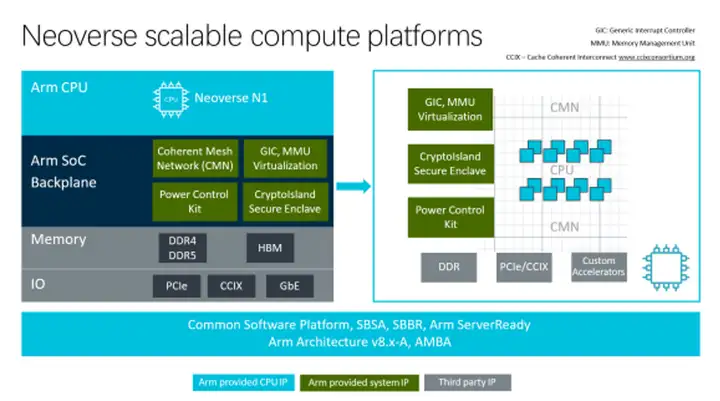

对亚马逊(Annapurna Labs)、阿里巴巴(平头哥)和 Ampere 这有足够芯片设计能力的“3A”客户来说,Arm 的 Neoverse 平台提供了设计一款服务器 CPU 的基础,包括 CPU 核心的微架构和配套的制程。

Arm 对服务器 CPU 市场的正面进攻可以回溯到 2011 年 10 月,Arm 发布加入可选 64 位架构(AArch64)的 ARMv8-A。一年后,Arm 发布实现 ARMv8-A 64 位指令集的微架构 Cortex-A53 和 Cortex-A57,AMD 表态将推出相应的服务器产品——后者多年的服务器市场经验正是当时的 Arm 阵营所稀缺的。

此后的几年中,芯片供应商如 Cavium、高通(Qualcomm)和国内的华芯通,超大规模用户如微软,都曾积极的推动 64 位 Arm 进入数据中心市场。但是,真正比较成规模化的部署,应当始自 2018 年 11 月 AWS 预览其首个 Arm 服务器 CPU —— Graviton。

Graviton 基于 2015 年推出的 Cortex-A72(A57 的继任者),16nm 制程,16 核、16 线程, 与同时期的 x86 服务器 CPU 比起来,颇有些‘“平平无奇”,最大的仰仗是亚马逊“自家的孩子”,可以充分优化。

Cortex-A 家族已经是 Cortex 三兄弟里最追求性能的了,但毕竟不是面向服务器平台的产品,不能放宽功耗限制去飙性能。于是,在Graviton 公开之前一个月,Arm 发布了面向云计算和边缘基础设施的 Neoverse 平台,起点便是 16nm 的 A72 和 A75,代号 Cosmos。

△ Neoverse可伸缩计算平台

仅仅 4 个月之后,2019 年 2 月,Arm 更新了 Neoverse 平台的路线图,推出 7nm 的 Neoverse N1,性能比之前的目标又有 30% 以上的提升。

代号 Ares 的 Neoverse N1,基础是 2018 年推出的 Cortex-A76,两者的流水线结构相同, 均为 11 级短流水线设计,前端都是 4 宽的读 取 / 解码器。Arm 将其称为“手风琴”管道,因为根据指令长度不 同,它可以在延迟敏感的情况下将第二预测阶段与第一获取阶段重 叠,将调度阶段与第一发布阶段重叠,将流水线长度减少到 9 级。L2 Cache 也新增可选的 1MiB 容量,是 A76 的 2 倍。

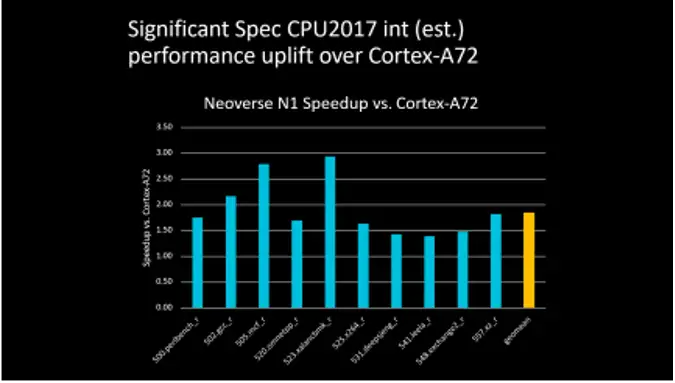

△ 4 vCPU 配置,Neoverse N1 相对 Cortex-A72的整数性能提升

相较于上一代的 A72 平台,Neoverse N1 平台带来了显著的性能提升, 许多项目的成绩翻倍,尤其是在标志性的机器学习项目中,成绩接 近上一代产品的 5 倍。虽然 A72 的年头早了点儿,但这样的性能差 距也说明 Neoverse N1 确实有了质的飞跃。

Graviton2 与 Altra 系列

Neoverse N1 平台带给数据中心市场的冲击很大,因为所有人都看 到了它的巨大潜力和价值,以及这背后的机会。如果说之前的 A72 还只是在数据中心市场崭露头角的话,那么 Neoverse N1 则让更多 人相信 Arm 有能力在这个领域分一杯羹。

两款分别来自云服务商和独立 CPU 供应商的 7nm CPU,都基于 Neoverse N1。

2019 年 11 月,AWS 官宣 Graviton2 处理器:

核数暴涨至 64,是一代的 4 倍;

晶体管数更有 6 倍,达到 300 亿之多;

64MiB L2 Cache,是一代的 8 倍;

DDR4-3200 内存接口,(频率)是一代的 2 倍;

运行频率 2.5GHz,略高于一代的 2.3GHz。

△ 2020 年 AWS 新增的 EC2 实例中, Gravtion2 占据半壁江山, Intel 和 AMD 的比例也耐人寻味

基于 Graviton2 的 EC2(Elastic Compute Cloud,弹 性 计 算 云)实 例类型迅速增多,包括但不限于通用型(M6g、T4g)、计算优化 型(C6g)、内存优化型(R6g、X2gd),部署的区域(Region)和数量也从 2020 年中起稳定增长——据统计,2020 年全年,AWS EC2 实例增量中的 49% 基于 AWS Graviton2。

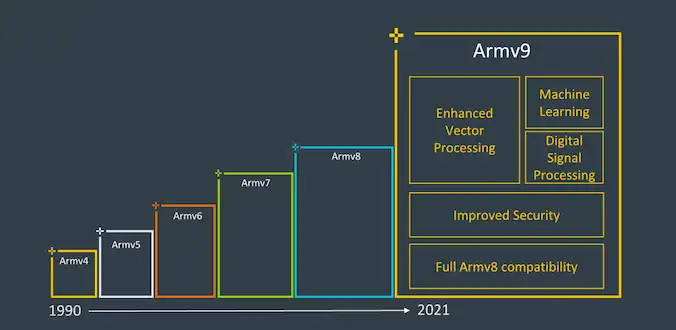

Armv9:继往开来

2011 年 11 月公布的 Armv8,将 Arm 带入了 64 位时代。在 Arm 与生态合作伙伴的共同努力下,经过数次产品迭代,Arm 阵营用了十年的时间,在服务器市场站稳了脚跟。

2021 年 3 月底,Armv9 发布,在 Armv8 的基础上,着重升级了安全性、 机器学习(Machine Learing,ML)和数字信号处理(Digital Signal Processing,DSP)方面的能力。

在新架构所带来的三大特性中,机器学习或许是大众最熟悉也是最关心的内容。伴随着异构应用的崛起,以机器学习为代表的人工智能(Artificial Intelligence,AI)技术已经深入我们生活的方方面面,无论是在后端的数据中心还是在终端、边缘侧,机器学习都大有用武之地。

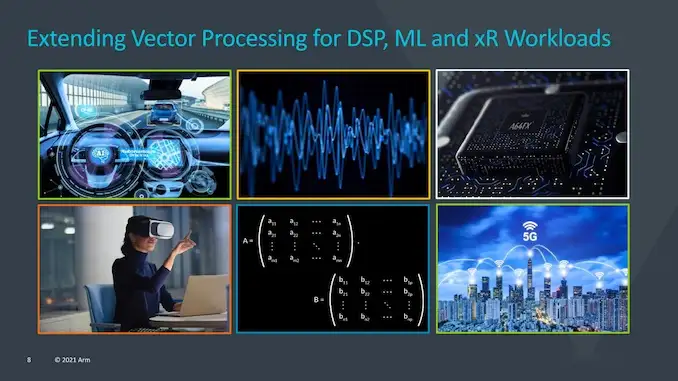

为了更好地提升 AI 和 DSP 所需的算力,ARMv9 将原本支持的可伸缩矢量扩展(Scalable Vector Extension,SVE)升级到了 2.0 版本。这项技术可以改善机器学习和数字信号处理应用的性能表现,有助于对 5G 系统、VR/AR、机器学习等一系列工作负载的处理。

SVE2 提供了可调节的向量(Vector,矢量)大小,范围从 128b(bit, 位)到 2048b,从而允许向量的可变粒度为 128b,这种变化并不会受到硬件平台的影响。这就意味着,软件开发人员将只需要编译一次其代码,就可以适用于 Armv9 乃至于后续产品中,实现“编写一次,到处运行”。同样,相同的代码将能够在具有较低硬件执行宽度能力的更保守的设计上运行,这对于 Arm 设计从物联网、移动到数据 中心的 CPU 而言至关重要。

SVE2 扩展还增加了压缩和解压缩 CPU 核心内的代码和数据的能力,因为将数据移入和移出芯片的过程耗电很大,尽可能多使用芯片内的数据可以减少这种数据移动,从而降低能耗。

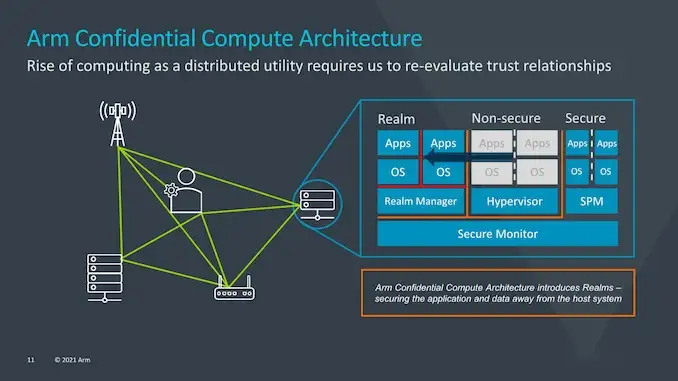

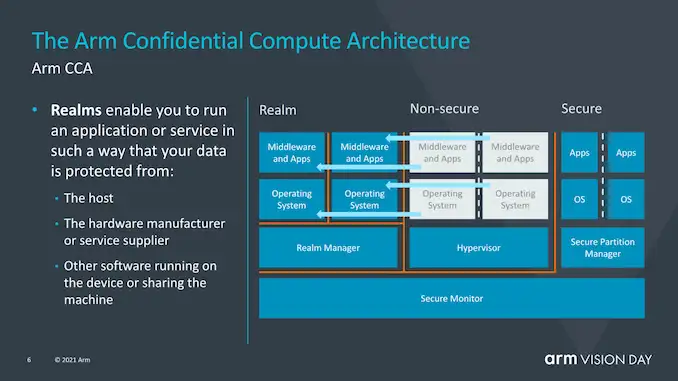

更值得一提的是 Confidential Compute Architecture(CCA),中文名称为机密计算架构,这也是 Arm 本次版本更新最重要的内容。其实安全问题近些年变得愈演愈烈,勒索病毒与黑客攻击无时无刻不在活动。面对层出不穷的网络攻击问题,既需要网络服务商、软件公司的努力,也需要包括 Arm 在内的硬件基础设施提供商从源头上封堵可能存在的漏洞,就促成了 CCA 的出现。这是一种基于架构层面的安全防护能力,通过打造基于硬件的安全运行环境来执行计算,保护部分代码和数据,免于被存取或修改,乃至不受特权软件的影响。

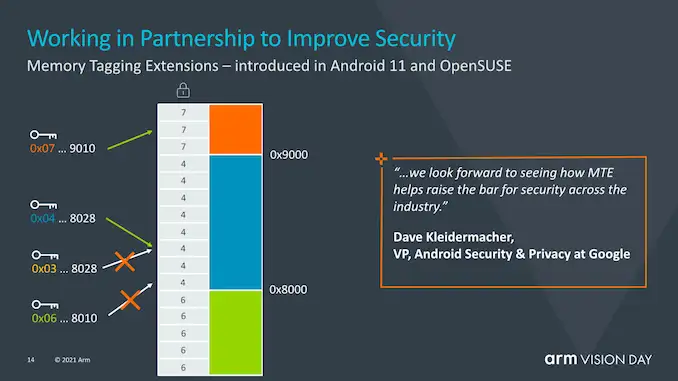

△ Arm 机密计算架构(左),Android 11 和 OpenSUSE 引入的内存标签扩展技术(右)

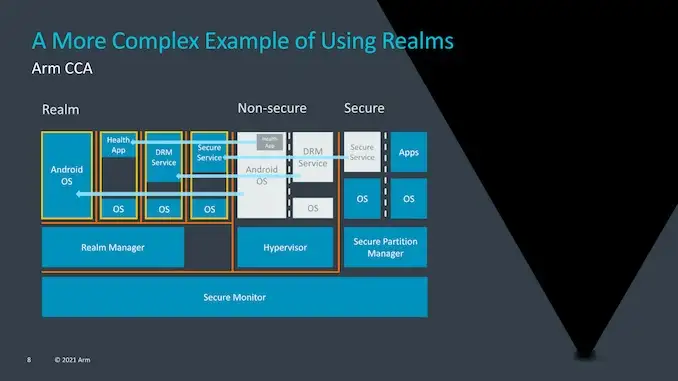

为此 CCA 引入了动态创建机密领域(Realms)的概念——这是一个安全的容器化执行环境,支持安全的数据操作,可将数据与 hypervisor 或操作系统隔离。Hypervisor 的管理功能由“领域管理器” (realms manager)承担,而 hypervisor 本身只负责调度和资源分配。使用“领域”的优势在于极大地减少了在设备上运行给定应用程序的信任链,操作系统在很大程度上对安全问题变得透明,也允许需要监督控制的关键任务应用程序能够在任何设备上运行。

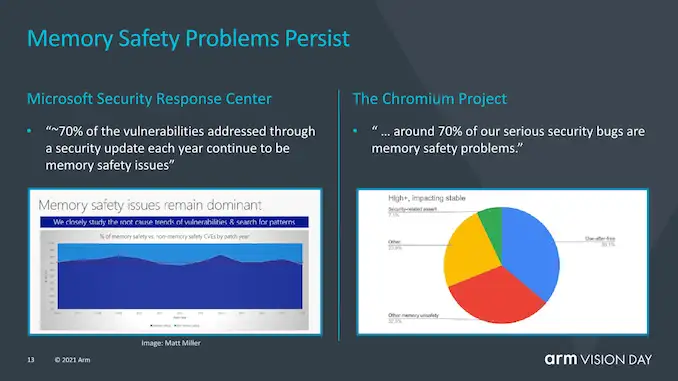

在实际应用中,内存是非常容易被攻击的一环,内存安全也一直成为行业的关注点,如何在内存安全漏洞被利用之前就能发现问题,是提高全球软件安全的重要一步。为此,Arm 与 Google 持续合作开发的“内存标签扩展”(MTE)技术也成为 Armv9 的一个组成部分,可在软件中查找内存的空间和时间安全问题,将指向内存的指针和标签建立联系,并在使用指针时检查这个标签是否正确。如果存取超过范围,标签检查就会失败,从而可以在第一时间发现内存安全漏洞并进行封堵。

Arm架构升级,v9与v8版本有何差异?

在过去多年里,Arm对ISA进行了改进,也对体系结构进行了各种更新和扩展。当中一些可能很重要,有些可能也是一瞥而过。

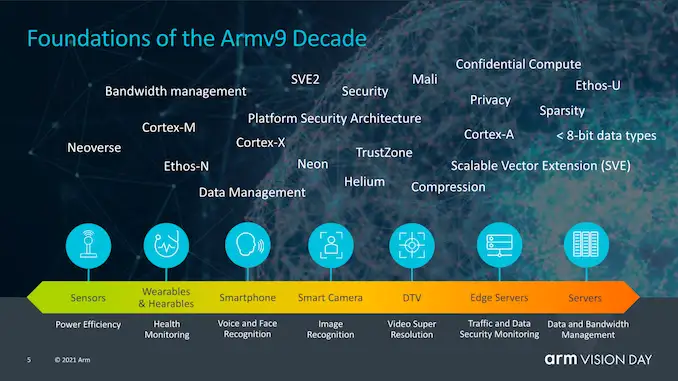

近日,作为Arm的Vision Day活动的一部分,该公司正式发布了该公司的新一代Armv9架构的首个细节,为Arm未来十年内成为下一个3000亿芯片的计算平台奠定了基础。

读者可能会问的一个大问题是,Armv9与Armv8究竟有何不同,能让架构获得如此大的提升。确实,从纯粹的ISA角度来看,v9可能不像v8相比v7那样实现根本性的跳跃,后者引入了AArch64,一个完全不同的执行模式和指令集,该指令集与AArch32相比具有更大的微体系结构分支,例如扩展寄存器,64位虚拟地址空间和更多改进。

Armv9继续使用AArch64作为基准指令集,但是在其功能上增加了一些非常重要的扩展,以保证architecture numbering的增加,并且允许Arm不仅可以获得对AArch64进行某种软件重新基准化v9的新功能,还能保持我们多年来在v8上获得的扩展。

Arm认为新架构Armv9有三个主要支柱,即安全性、AI以及改进的矢量和DSP功能。对于v9,安全性是一个非常重要的主题,我们将深入探讨新扩展和功能的新细节,但是首先谈到的DSP和AI功能应该很简单。

新的Armv9兼容CPU所承诺的最大的新功能可能是开发人员和用户可以立即看到的——SVE2作为NEON的后继产品。

可伸缩矢量扩展(SVE)的于2016年首次亮相,并首次在富士通的A64FX CPU内核中实现,该芯片已为日本排名第一的超级计算机Fukagu提供支持。SVE的问题在于,新的可变矢量长度SIMD指令集的第一次迭代的范围相当有限,并且更多地针对HPC工作负载,缺少了许多仍由NEON涵盖的更通用的指令。

SVE2于2019年4月发布,旨在通过用所需指令补充新的可扩展SIMD指令集来解决此问题,以服务于类似DSP等目前仍在使用NEON的工作负载。

除了增加的各种现代SIMD功能外,SVE和SVE2的优势还在于其可变的向量大小,范围覆盖了128b到2048b,让其无论在什么硬件运行,都允许向量的可变粒度为128b。如果纯粹从向量处理和编程的角度来看,这意味着软件开发人员将只需要编译一次其代码,并且如果将来某个CPU带有本地的512b SIMD execution pipelines,该代码将能够充分利用单元的整个宽度。同样,相同的代码将能够在具有较低硬件执行宽度能力的保守设计上运行,这对于Arm设计从物联网、移动到数据中心的CPU而言至关重要。在保留Arm体系结构的32b编码空间的同时,它还可以完成所有这些工作。然而类似X86这样的架构则需要根据矢量尺寸增加新的指令和扩展。

机器学习也被视为Armv9的重要组成部分,因为Arm认为在未来几年中,越来越多的ML工作负载将变得司空见惯,当中包括了对性能或电源效率有至关重要要求的场景中。那就让在专用加速器上运行ML工作负载变成长久的需要,与此同时,我们还会继续在CPU上运行较小范围的ML工作负载。

矩阵乘法指令(Matrix multiplication instructions )是此处的关键,它将代表生态系统中将更大范围采用v9 CPU作为基本功能所迈出的重要一步。

通常,我认为SVE2可能是保证升级到v9的最重要因素,因为它是更确定的ISA功能,可以在日常使用中与v8 CPU区别开来,并且可以保证软件生态系统能够正常运行,这与现有的v8堆栈有所不同。对于服务器领域的Arm来说,这实际上已经成为一个相当大的问题,因为软件生态系统仍在基于v8.0的软件包基础上,不幸的是,该软件包缺少了最重要的v8.1大型系统扩展。

使整个软件生态系统向前发展,并假设新的v9硬件具有新的体系结构扩展功能,这将有助于推动事情发展,并可能解决某些当前情况。

但是,v9不仅涉及SVE2和新指令,它还非常注重安全性,在安全性方面我们将看到一些更根本的变化。

介绍机密的计算架构

在过去的几年中,安全性和硬件安全性漏洞已成为芯片行业的头等大事,Spectre,Meltdown等漏洞的出现及其所有同级边信道攻击都表明,重新思考如何保证安全成为了一个基本需求。Arm希望用来解决这一总体问题的方法是通过引入Arm机密计算体系结构(Arm Confidential Compute Architecture:CAA)来重新设计安全应用程序的工作方式。

在继续之前,我想提箱一下,今天的披露仅仅是对新CCA运作方式的高层次解释,Arm说,有关新安全机制的确切工作原理的更多细节将在今年夏天的晚些时候公布。

CCA的目标是从当前的软件堆栈情况中获得更大的收益,在当前的软件堆栈情况下,在设备上运行的应用程序必须固有地信任它们所运行的操作系统和虚拟机管理程序。传统的安全模型是基于以下事实建立的:更高特权的软件层被允许查看较低层的执行,然而当操作系统或系统管理程序被以任何方式损害时,这就可能成为了一个问题。

CCA引入了动态创建““realms”的新概念,可以将其视为对OS或虚拟机管理程序完全不透明的安全容器化执行环境。系统管理程序将仍然存在,但仅负责调度和资源分配。而“realm”将由称为“ealm manager”的新实体管理,其被认为是一段新的代码,大致大小约为hypervisor的1/10。

realm内的应用程序将能够“证明”领域管理器以确定其是否可信任,这对于传统的虚拟机管理程序而言是不可能的。

Arm并没有深入探讨究竟是什么造成了realm与操作系统和虚拟机管理程序的非安全世界之间的这种隔离,但听起来确实像硬件支持的地址空间,但它们无法相互交互。

使用realms的优势在于,它极大地减少了设备上运行的给定应用程序的信任链,并且OS对安全性问题变得越来越透明。与当今需要企业或企业使用带有授权软件堆栈的专用设备的情况相反,需要监督控制的关键任务应用程序将能够在任何设备上运行。

MTE(memory tagging extensions)并不是v9的新功能,而是随v8.5一起引入的,MTE或内存标记扩展旨在帮助解决世界软件中两个最持久的安全问题。缓冲区溢出(Buffers overflows)和无用后使用(use-after-free)是持续的软件设计问题,在过去的50年中,这些问题一直是软件设计的一部分,并且可能需要花费数年的时间才能对其进行识别或解决。MTE旨在通过在分配时标记指针并在使用时进行检查来帮助识别此类问题。

未来的Arm CPU路线图

这与v9没有直接关系,但是与即将到来的v9设计的技术路线图紧密相关,Arm还谈到了有关他们在未来2年中对v9设计的预期性能的一些观点。

Arm谈到了移动市场在今年如何将带有X1的设备性能提升了2.4倍(此处我们仅指ISO流程设计的IPC),该性能是几年前推出的Cortex-A73的两倍。

有趣的是,Arm还谈到了Neoverse V1设计及其如何达到A72类似设计性能的2.4倍,并透露他们期待着他今年晚些时候发布的首批V1设备。

对于代号为“ Matterhorn”和“ Makalu”的下一代移动IP内核,该公司公开了这两代产品的合计预期IPC增益为30%,其中不包括SoC设计人员可以获得的频率或任何其他其他性能增益。这实际上代表着这两种新设计的世代增加了14%,并且如幻灯片中的性能曲线所示,这表明相对于自A76以来Arm在过去几年所管理的工作而言,改进的步伐正在放缓。不过,该公司指出,进步速度仍然远远超过行业平均水平。但潭门也坦言,这被一些行业参与者拖累了。

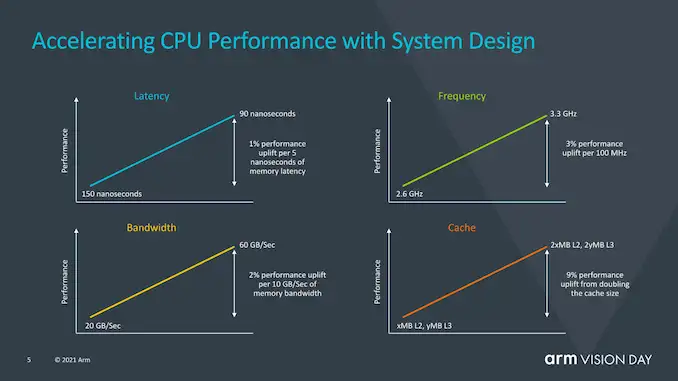

Arm还提供了一张很有意思的幻灯片,该幻灯片旨在关注系统侧对性能的影响,而不仅仅是CPU IP性能。从这里提供的一些数据可以看到,例如每5ns的内存延迟中有1%的性能,这是我们现在已经广泛讨论了几代的数字,但是Arm在这里还指出,排除了是否通过改善内存路径,增加缓存或优化频率功能来改善实现的其他各个方面,他们可以使用整整一代的CPU性能提升,我认为这是对SoC供应商当前保守方法的一种评价,这些方法没有充分利用X1内核的预期性能余量,并且随后也未达到新内核的预期性能预测。

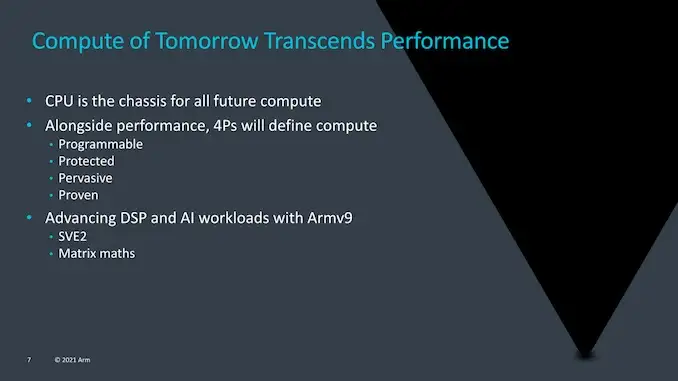

Arm继续将CPU视为未来最通用的计算模块。尽管专用的加速器或GPU将会占有一席之地,但它们很难解决一些重要问题,例如可编程性,保护性,普遍性(本质上是在任何设备上运行它们的能力)以及经过验证的正常工作的能力。当前,计算生态系统在运行方式上极为分散,不仅设备类型不同,而且设备供应商和操作系统也不同。

SVE2和Matrix乘法可以极大地简化软件生态系统,并允许计算工作负载以更统一的方法向前迈进,该方法将来将可以在任何设备上运行。

最后,Arm还分享了有关Mali GPU未来的新信息,并透露该公司正在开发VRS等新技术,尤其是Ray Tracing。这一点令人非常令人惊讶,也表明AMD和Nvidia引入RT推动的台式机和控制台生态系统也有望将移动GPU生态系统推向RT。

Armv9设计即将在2022年初面世

今天的公告以一种非常高级的形式出现,我们希望Arm在接下来的几个月中,在公司通常的年度技术披露中,更多地谈论Armv9的各种细节和新功能,例如CCA。

总的来说,Armv9似乎是更基本的ISA转变(可以看作SVE2)与软件生态系统的总体重新基准的结合,以汇总v8扩展的最后十年,并为下一个十年奠定基础Arm体系结构。

Arm于去年下半年已经谈论过Neoverse V1和N2,我确实希望N2至少最终是基于v9而设计发布的。Arm进一步透露,更多基于Armv9的 CPU设计(可能是移动端Cortex-A78和X1的后续产品)将于今年推出,而新的CPU可能已经被通常的SoC供应商所采用,并且有望成为在2022年初在商用设备中出现。

来源:E企研究院、半导体行业观察

10T 技术资源大放送!包括但不限于:Linux、虚拟化、容器、云计算、网络、Python、Go 等。在开源Linux公众号内回复10T,即可免费获取!Linux学习指南有收获,点个在看